True progress starts with the right partnership. We work closely with you

to understand your challenges

and deliver efficient solutions.

Talent Scarcity

Bridge the semiconductor talent gap by augmenting small teams with AI agents that deliver expert-level verification without requiring additional hiring.

Increasing Complexity

Deliver more complex designs

and multiple projects with your

existing engineering team.

Faster Tapeout

Gain market share by accelerating time to market with Moores Lab AI.

We offer

Optimized

for

efficiency

Moores Lab AI solutions outperform traditional chip design processes with unmatched cost efficiency.

Transform Your Business

IP verification package.

Kick-Off & Requirements

IP Analysis & Qualification

Evaluation Metrics

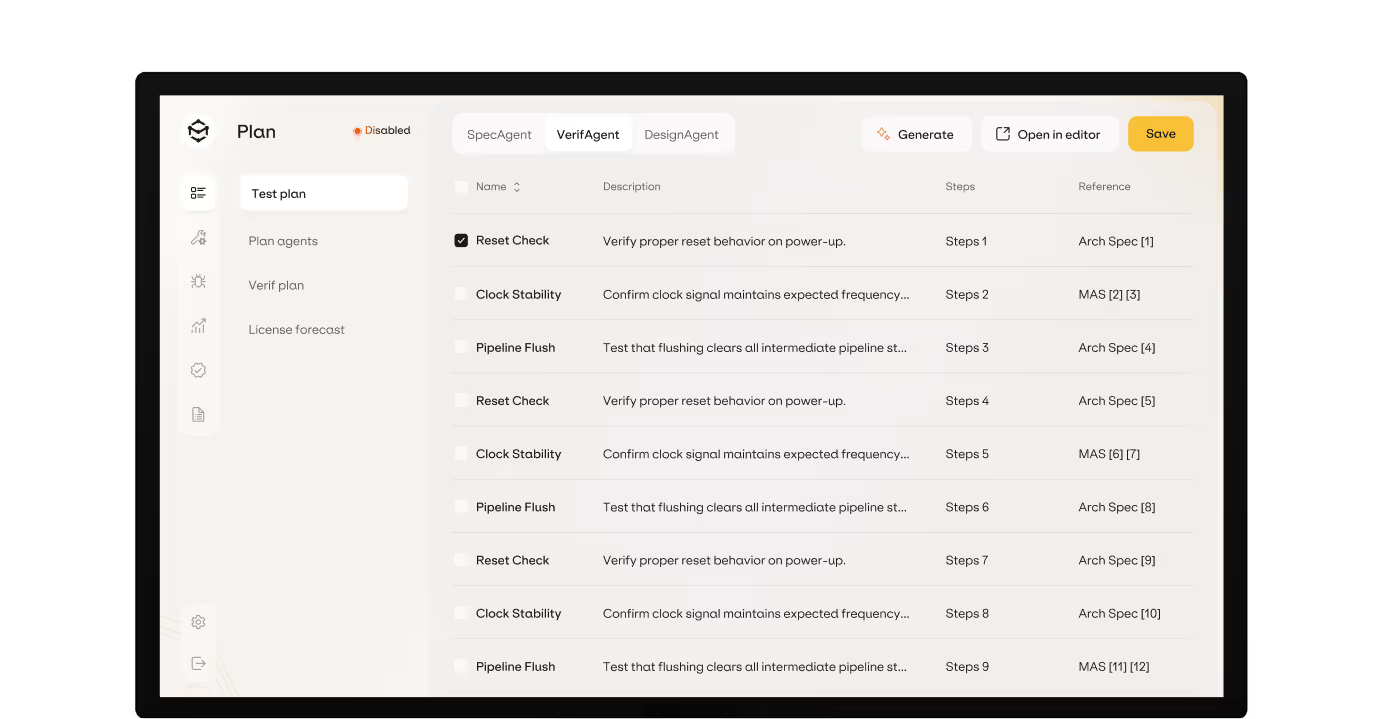

Test Plan Generation

Test Bench Generation

Test Cases (Stimulus Generation)

Final Delivery

Testimonials

silicon engineering

meet our

advisors

shaping the future of AI and silicon.

resources

We're here

to help.

FAQ

Who founded Moores Lab AI?

Moores Lab AI was founded in 2025 by Shelly Henry, Shashank Chaurasia, and Sirish Munipalli — industry veterans with over 45 years of combined semiconductor experience and 10+ years in applied AI.

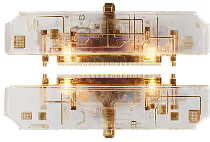

What is VerifAgentTM?

VerifAgentTM is our flagship AI-powered verification agent that automates the creation of test plans, UVM testbenches, test cases, scoreboards, functional coverage, and assertions.

What parts of the chip development lifecycle does Moores LabAI support?

We support the IP block silicon development flow:

- Architecture specification

- RTL design

- Functional verification

- Simulation & debug

- Coverage analysis

Does VerifAgentTM work with existing EDA tools?

Yes. VerifAgentTM integrates seamlessly with all major EDA tools including Synopsys, Cadence, and Siemens. No reformatting, retraining, or workflow changes are required.

Can I deploy Moores LabAI on-premise?

Yes. Our agentic AI is deployed on-premise. We support LLM connection to Azure OpenAI and AWS Anthropic in the cloud depending on your security needs. On-prem LLM deployment is supported for IP-sensitive environments.

What kind of ROI can I expect?

Customers typically see:

- 92–97% productivity gains

- 150–200+ engineering hours saved per project

- 1–5 critical bugs caught early

What are the cost savings for verification?

VerifAgentTM reduces verification costs by up to 86%. Manual UVM verification that typically takes 6–12 months can now be completed in under a month.

Who are our ideal customers?

Small-to-mid-to-large semiconductor companies designing custom SoCs, Sub-Systems, or IP blocks. Startups building advanced silicon (e.g., photonic or quantum chips) or FPGAs are also a great fit.

What if I don’t want to adopt a new tool?

We offer Verification-as-a-Service. You provide your IP and specs, and we deliver a complete UVM environment in <45 days.

What LLMs do you use?

Our platform is LLM-agnostic and supports Azure OpenAI, AWS Anthropic, Mistral, Llama, and more. We also support MooreLLM (custom) for on-premises deployment, depending on your security needs.

How do you handle IP security?

Moores Lab AI takes intellectual property (IP) security extremely seriously, offering multiple layers of protection tailored to the needs of semiconductor companies:

- On-Premise Deployment for Maximum Control: Moores Lab AI offers an on-premise deployment option that allows customers to run the entire platform within their own secure infrastructure. This ensures that sensitive IP never leaves the customer’s environment and remains fully under their control.

- Strict Access Control and Data Isolation: The platform is architected with session-based and user-level isolation, so data from one project or user cannot be accessed by others. This sandboxed design ensures IP segregation and minimizes risk of data leakage across sessions or users.

- LLM Security and Compliance: When using cloud-based large language models (LLMs) like OpenAI, Moores Lab AI ensures compliance with OpenAI’s “Zero Data Retention” mode, which prevents training on customer data and deletes logs after 30 days. Customers also have the option to avoid features that store application state (like threads or assistants).

- No Use of Web Tools or External Content Fetching: VerifAgentTM does not use OpenAI’s web search or third-party tools like Remote MCP, which could potentially expose IP to the public internet. Instead, it only uses “file search” within user-provided documents.

- Optional IP Whitelisting and Firewall Configuration: Customers can implement firewall-level IP whitelisting for all external API endpoints used (e.g., OpenAI and Cryptlex licensing), ensuring controlled and monitored data egress.

- No API/SDK Exposure: Moores Lab AI does not expose public APIs or SDKs for its platform, further minimizing the surface area for external access to sensitive data.

In summary, Moores Lab AI offers a robust, enterprise-grade IP protection framework combining on-premise deployment, secure LLM integration, fine-grained access control, and zero external data exposure — making it ideally suited for high-security semiconductor environments.

What’s the typical onboarding process?

A standard engagement includes:

- Kick-off & Requirements

- IP Analysis

- Success Metric Agreement

- Test Plan & Bench Generation

- Stimulus Generation

- Delivery & Handoff

The entire flow takes <1 month, with most steps completed in hours

How can I evaluate Moores LabAI?

We offer pilots to prove value before a full rollout. You can book a meeting at calendly.com/mooreslab/30min.

What’s required from my side for a pilot?

You'll need to provide:

- Architecture & micro-architecture specs

- RTL (can be incomplete or buggy)

- Access to your preferred EDA tools

- Evaluation metrics and goals