Moores Lab AI is proud to announce a formal partnership with Breker Verification Systems to deliver the industry’s first AI-driven SoC verification flow integrating Breker’s Trek Test Suite Synthesis with our agentic AI platform, VerifAgent™. Together, we are enabling automated specification-to-test generation across complex, multi-core SoC designs, bridging C, SystemVerilog, simulation, and emulation environments in a unified workflow.

By combining Breker’s production-proven test synthesis expertise with Moores Lab AI’s multi-agent orchestration and autonomous verification loops, engineering teams can generate high-coverage scenario tests directly from written specifications faster, more consistently, and with greater confidence.

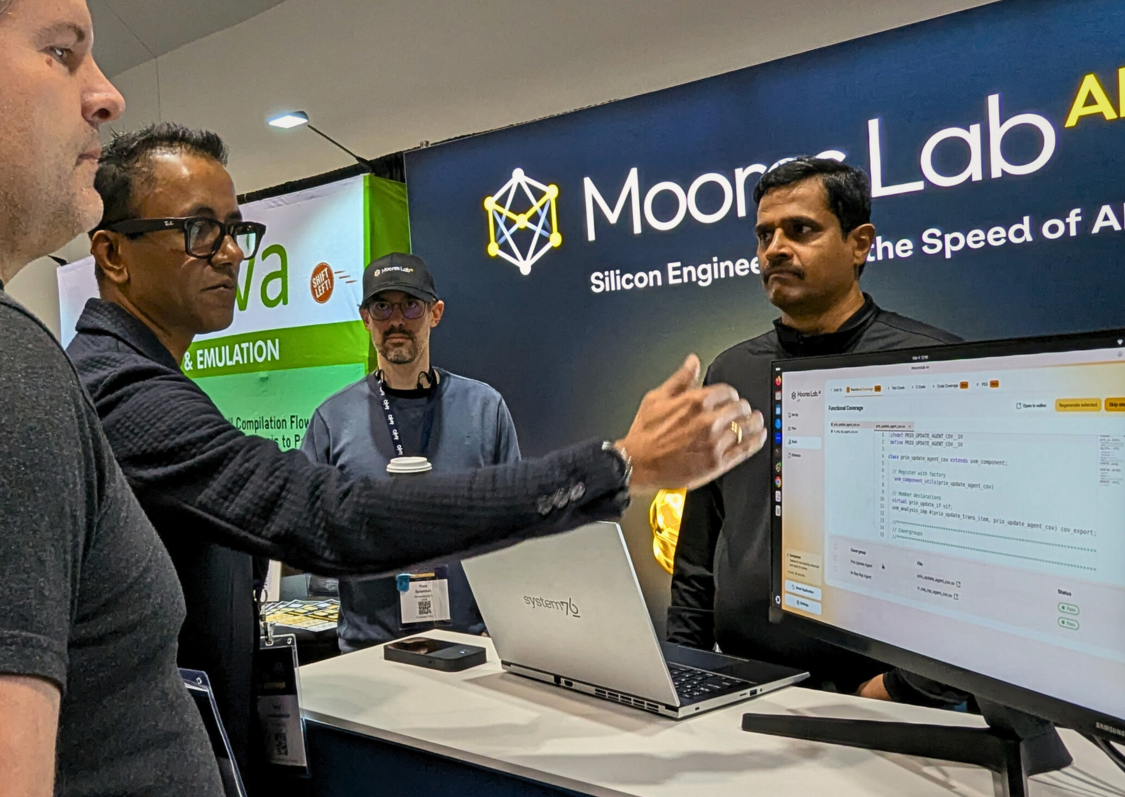

This collaboration was formally kicked off at DVCon U.S. 2026, in a panel on SoC Verification where our CEO Shelly Henry joined a panel of industry leaders shaping the future of AI-driven verification. The discussion featured Adnan Hamid, CTO of Breker Verification Systems; Deepak Manoharan, Senior Director at Arm Ltd.; and Michael Chin, Senior Principal Engineer at Intel Corporation. Together, they addressed a central challenge in modern silicon engineering: how to scale verification intelligently as SoC architectures grow more complex and traditional tool flows become increasingly resource-intensive.

The joint solution leverages agentic AI to interpret specifications, generate scenario models, and feed Breker’s synthesis engine to produce comprehensive, high-coverage tests across diverse verification platforms. The result goes beyond incremental improvement to create a structural shift in how verification plans are created and executed. A prototype of the integrated flow was demonstrated live at DVCon, marking the beginning of a broader 2026 rollout. This partnership represents a shared commitment to making AI practical, production-ready, and deeply aligned with the realities of semiconductor verification.

For more details, see the article in Semiconductor Digest.